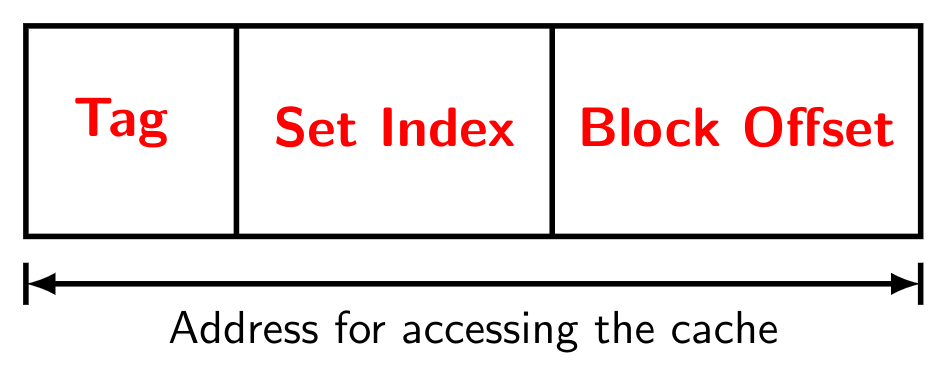

$32$ bit address is used for accessing the cache.

It is given that cache is Set-Associative.

The address bits get split as follows:

Block Size $= 64 B \implies$ Block offset $= 6\; bits.$

Given that Tag field width $= 22\; bits.$

Therefore, width of Set Index field $= 32-22-6 = 4 \implies 2^4\text{ = 16 sets in the cache.}$

Cache size is $2 KB$ and Block size $= 64 B$ $\implies 2^5 \text{ = 32 blocks present in the cache. }$

$16$ sets contain $32$ blocks $\implies 2$ blocks per set or associativity $=2.$

Correct Answer: $2$